अनुरूप संकेत (एनालॉग सिग्नल) , analog signal in hindi क्या है , परिभाषा , एनालॉग सिग्नल और डिजिटल सिग्नल में अंतर

तार्किक द्वार (लॉजिक गेट)

A + B

|

निवेशी

|

संकेत

|

निर्गत संकेत

|

|

A

|

B

|

Y = A + B

|

|

0

|

0

|

0

|

|

1

|

0

|

1

|

|

0

|

1

|

1

|

|

1

|

1

|

1

|

OR gate का स्विच परिपथ चित्र :-

A.B

|

निवेशी

|

संकेत

|

निर्गत संकेत

|

|

A

|

B

|

Y = A.B

|

|

0

|

0

|

0

|

|

1

|

0

|

0

|

|

0

|

1

|

0

|

|

1

|

1

|

1

|

|

निवेशी संकेत

|

निर्गत संकेत

|

|

A

|

Y = A’

|

|

0

|

1

|

|

1

|

0

|

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

|

|

A

|

B

|

A + B

|

Y = (A+B)’

|

|

0

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

|

1

|

1

|

1

|

0

|

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

|

|

A

|

B

|

A .B

|

Y = (A.B)’

|

|

0

|

0

|

0

|

1

|

|

1

|

0

|

0

|

1

|

|

0

|

1

|

0

|

1

|

|

1

|

1

|

1

|

0

|

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

||||

|

A

|

B

|

A’

|

B’

|

A.B’

|

A’B

|

Y=A.B’ + A’B

|

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

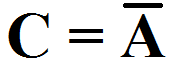

NOR गेट से NOT गेट (nor to not gate conversion) :

सत्यता सारणी :

|

निवेशी संकेत

|

निर्गत संकेत

|

|

A

|

Y = A’

|

|

0

|

1

|

|

1

|

0

|

NOR gate से OR गेट रूपांतरण (nor to or gate conversion):

सत्यता सारणी :

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

||

|

A

|

B

|

A+B

|

(A+B)’

|

Y = (A+B)” = A+B

|

|

0

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

1

|

1

|

0

|

1

|

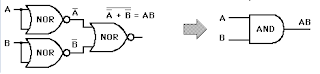

NOR gate से AND गेट बनाना (nor to AND gate conversion) :

सत्यता सारणी :

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

|||

|

A

|

B

|

A’

|

B’

|

A’+B’

|

Y = (A’+B’)’

|

|

0

|

0

|

1

|

1

|

1

|

0

|

|

1

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

0

|

|

1

|

1

|

0

|

0

|

0

|

1

|

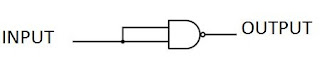

NAND गेट से NOT गेट का निर्माण :

सत्यता सारणी :

|

निवेशी संकेत

|

निर्गत संकेत

|

|

A

|

Y = A’

|

|

0

|

1

|

|

1

|

0

|

NAND गेट से AND गेट का निर्माण :

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

||

|

A

|

B

|

A.B

|

(A.B)’

|

Y = (A.B)” = A.B

|

|

0

|

0

|

0

|

1

|

0

|

|

1

|

0

|

0

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

1

|

1

|

1

|

0

|

1

|

|

निवेशी संकेत

|

निवेशी संकेत

|

निर्गत संकेत

|

|||

|

A

|

B

|

A’

|

B’

|

A’.B’

|

Y = (A’.B’)’

|

|

0

|

0

|

1

|

1

|

1

|

0

|

|

0

|

1

|

1

|

0

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

0

|

1

|

हिंदी माध्यम नोट्स

Class 6

Hindi social science science maths English

Class 7

Hindi social science science maths English

Class 8

Hindi social science science maths English

Class 9

Hindi social science science Maths English

Class 10

Hindi Social science science Maths English

Class 11

Hindi sociology physics physical education maths english economics geography History

chemistry business studies biology accountancy political science

Class 12

Hindi physics physical education maths english economics

chemistry business studies biology accountancy Political science History sociology

English medium Notes

Class 6

Hindi social science science maths English

Class 7

Hindi social science science maths English

Class 8

Hindi social science science maths English

Class 9

Hindi social science science Maths English

Class 10

Hindi Social science science Maths English

Class 11

Hindi physics physical education maths entrepreneurship english economics

chemistry business studies biology accountancy

Class 12

Hindi physics physical education maths entrepreneurship english economics